# Trabajo previo experiencia 3

#### José Miguel Saavedra 201804079-7

### 3.1 Investigación de conceptos

a) También llamado HDL, corresponde a un lenguaje de programación especializado que se utiliza para definir la estructura, diseño y operación de circuitos electrónicos, y más comúnmente, de circuitos electrónicos digitales, como el convertidor analógico-digital o cualquier antena satelital. haciendo posible una descripción formal de un circuito electrónico, y posibilitando su análisis automático y su simulación. Una de las diferencias más importantes que tiene con respecto a otros lenguajes de programación es que el HDL incluye explícitamente la noción de tiempo.

b)Wire es utilizado para conectar diferentes elementos, y pueden ser tratados como cables físicos. También pueden ser de lectura o asignados y no pueden almacenar información, a diferencia de reg que si puede almacenarla, además de que necesitan ser llevados por declaraciones de asignación continua o desde un puerto de un módulo. Reg es utilizado para almacenamiento de elementos en Verilog, y pueden retener el valor hasta que el próximo sea asignado (pero no a traves de declaración asignada), además, pueden ser sintetizados a flipflop, latch o circuitos combinacionales, lo cual provoca confusión debido a temas relacionados con hardware. Logic es como una versión mayor de reg y menos confusa, esta no permite multiples drivers y posee una asignación final que resuelve problemas en caso de asignaciones múltiples, lo cual da a entender que no posee una equivalencia de hardware, como ocurre en el caso de reg. En el caso de reg y wire, estos dan X si hay multiples drivers que intenten darle diferentes valores, mientras que logic solo asigna el último. También se diferencia de reg y wire debido a que logic puede ser controlado por el bloque de asignación, el output de un puerto y dentro de un bloque de procedimiento.

c) La diferencia entre circuitos lógicos secuenciales y combinacionales es que el primero depende de los ciclos del CLOCK y también de los inputos presentes y anteriores para generar un output, mientras que los combinacionales se definen como circuitos independientes del tiempo, ya que no dependen de los inputs anteriores para generar un output, además de que poseen una velocidad mayor y no hay un feedback entre el input y output.

d)

e) No afecta a la evaluación, ya que esta hecha en el momento, mientras que lo que será afectado por el delay será la asignación que se va a realizar.

## 3.2 Análisis de Código

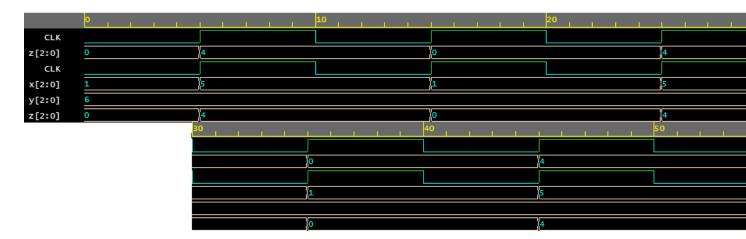

Como se ve en la imagen, las variables x, y, z van cambiando respectivamente de la siguiente forma:

- 1. Primera subida: x = 5, y = 6, z = 4

- 2. Segunda subida: x = 1, y = 6, z = 0

- 3. Tercera subida: x = 5, y = 6, z = 4

```

4. Cuarta subida: x = 1, y = 6, z = 0

```

5. Quinta subida: x = 5, y = 6, z = 4

Figure 1: Imagen del clock

### 3.3 Diseño de Módulo

1. Código

2. testbench

```

module tb_temporizador();

reg CLK;

reg rstn;

wire [3:0] out;

always #5 CLK = ~CLK;

```

```

initial begin

$dumpfile("dump.vcd"); $dumpvars;

CLK <= 0;

rstn <= 0;

#20    rstn <= 1;

#80    rstn <= 0;

#50    rstn <= 1;

#20 $finish;

end

endmodule</pre>

```