#### Pre-Informe 3

# INF-245: Arquitectura y Organización de Computadores

Nicolás Farías G. 201773106-0

#### Pregunta 1

- a) Un lenguaje de descripción de hardware o simplemente HDL es un lenguaje especializado de computadora que se utiliza para describir la estructura y comportamiento de circuitos electrónicos y circuitos digitales lógicos. Un lenguaje de programación sirve para crear software, en cambio el HDL está diseñado para representar hardware.

- b) logic: Sirve para representar una variable booleana, puede tomar valores de 0, 1, floating o undefined. Debe ser usado en todas partes excepto donde hay señales con múltiples controladores.

reg: Sirve para representar la salida de un flip-flop, un latch o lógica combinacional.

wire: Sirve para representar lógica combinacional, o una red cuando hay solo un controlador.

La principal diferencia es que reg y wire estan obsoletas en SystemVerilog siendo reemplazadas por logic. En Verilog, las señales al lado izquierdo de <= o = en un bloque always debian ser declaradas como reg y todas las otras señales por defecto son de tipo wire.</li>

- c) La sentencia assign se utiliza fuera del bloque always y sirve para describir lógica combinacional simple, se evalúa concurrentemente, es decir, se reevalua cada vez que las entradas cambian.

La asignación <= (llamada asignación de no bloqueo) se utiliza dentro de el bloque always y es una buena practica usarla para representar lógica secuencial, también es concurrente.</li>

La asignación = (llamada asignación de bloqueo) se utiliza para representar lógica combinacional más compleja dentro del bloque always, no se evalúa concurrentemente.

- d) reg define que la señal va a ser de tipo lógico, [15:0]g nos dice que es un bus de 16 bits. Luego se le asigna a la señal el valor hexadecimal de 16 bits A6B2 como nos indica la letra h al frente de la expresión. El valor binario es 1010 0110 1011 0010.

- e) Primero first obtiene el valor 1, ya que tiene una asignación de no bloqueo, luego con esta señal se selecciona el elemento en la posición 1 de arr, el cual se reemplaza por su valor negado.

## Pregunta 2

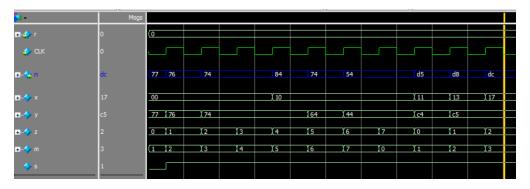

Primero le asignamos un valor a r de 000. Luego se realiza el ruteo en ModelSim siguiendo el valor de n (Los valores en la imagen estan en hexadecimal). Como se ve en la simulación n termina con un valor de dc =  $1101 \ 1100$ .

Ruteo

### Pregunta 3

endmodule

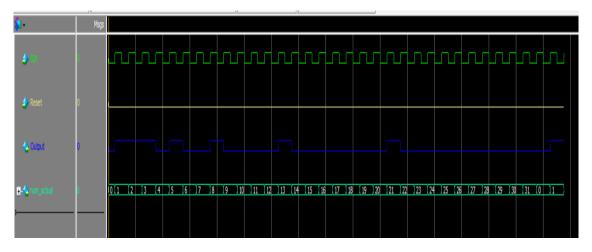

Se adjunta el código System Verilog y su simulación con una vuelta completa del contador, es decir, de 0 a 31 y luego se reinicia. Se puede observar que s está en 1 cada vez que n es un número de fibonacci. Los números estan en formato decimal por claridad.

Simulación del código